- 全部

- 默认排序

本次直播是allegro七月特训班第三次直播,截止到目前为止,软件部分已经学完了,本次直播主要是由黄老师来总结一下软件部分的学习情况以及答疑解惑,对大家的软件部分遇到的问题进行剖析,以及分享大家的软件学习总结。

有人说,公司招聘员工进来工作,支付报酬,员工自然有义务为公司提供相应的价值,那么去掉工作之外,公司有必要给员工提供岗位技能培训吗?答案自然是显而易见,尤其是对于很多正处于创作疲倦期的电子工程师来说,更无需单独领出来发问!公司正常招人,不能奢

在电子设计领域,Pads和Allegro是电子工程师常用的两种EDA软件,有时候,工程师在面对项目设计时需要将Pads格式的文件转换为Allegro格式,以便与其他团队或供应商进行协作工作,所以本文将介绍一种方法,教你将将Pads文件转为A

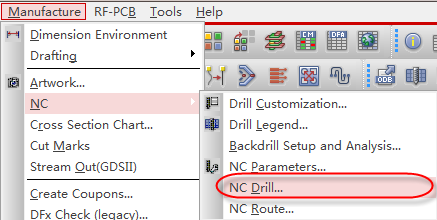

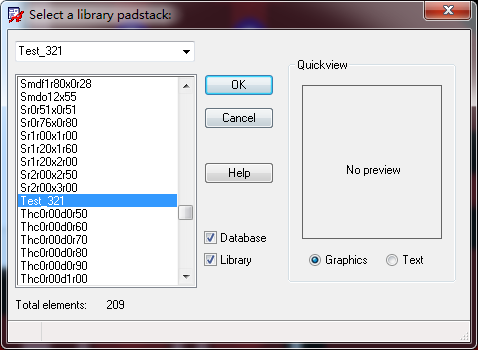

答:在使用Allegro软件,升级到16.6版本以后,会出现这样的问题,输出的钻孔数据文件,导入CAM350软件进行检查时,不识别钻孔的情况。我们这里讲述一下,如何去设置参数,让CAM350可以识别16.6版本输出的钻孔文件。

答:ICT (In Circuit Tester,自动在线测试仪)是印制电路板生产中重要的测试设备:用于焊接后快速测试元器件的焊接质量,能迅速定位焊接不良的引脚,以便及时进行补焊。体现在PCB设计上,则需要在设计中添加用于ICT测试的焊盘,并对符合测试点要求的焊盘添加测试点属性。因测试点焊盘和间距及位置有严格的要求,对于有ICT设计要求的板卡,建议在设计前就明确添加ICT的网络,拟定ICT的添加计划,在设计的过程中边布线边添加。如果在设计完后再添加ICT测试点,必将大量返工,甚至有的网络根本无法

答:在上述的问答中,我们对所有的区域的含义进行了详细的描述,下面我们讲述下在PCB设计中对一些常用的布局布线区域进行设置,首先在绘制好板框的情况下,我们以Route Keepin为例,然后运用z-copy命令进行设置,具体的操作如下:

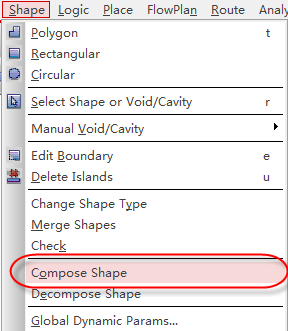

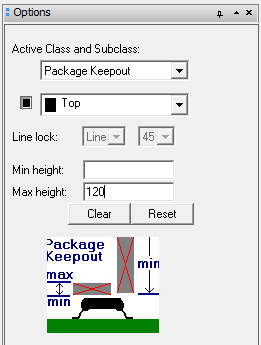

答:我们在进行一些复杂的PCB设计时,都会有很多结构限制,比如这里限高3MM等需求,为了辅助工程师们更好的进行设计,我们需要在PCB区域内绘制限高区域,并设置限高的参数,具体操作如下所示:第一步,在PCB板上绘制需要限高的区域,执行菜单命令Setup-Areas,在下拉菜单中选择Package Keepout,如图5-66所示,显示器件禁布区。

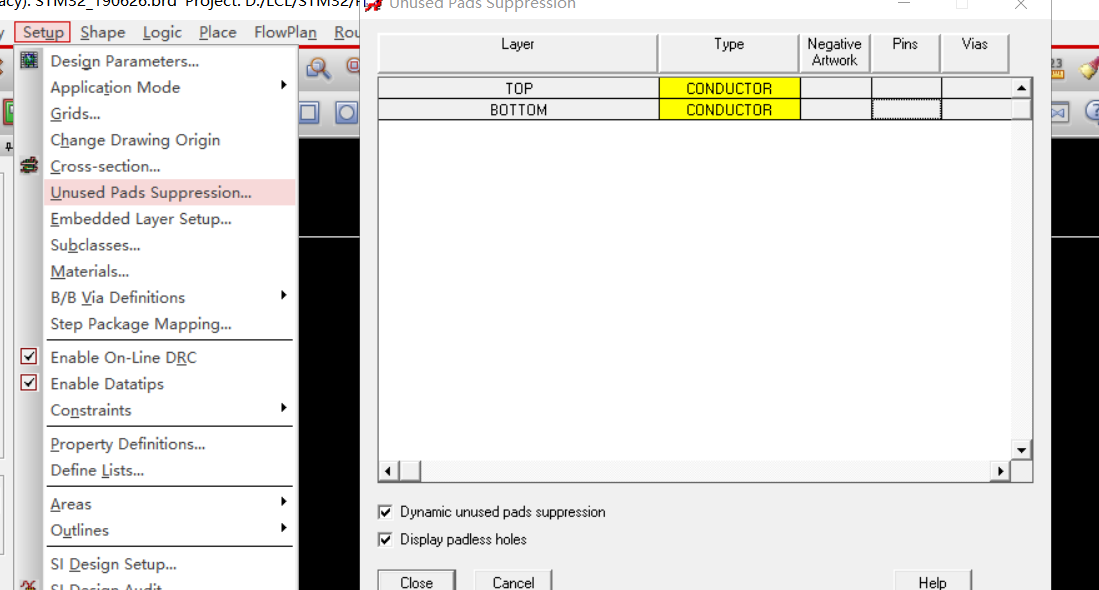

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

在pcb布局和布线时,有时般出线路板的外形图的时候结构设计会考虑到电路板的装配等问题,会限制原件摆在某个区域里面,走线也限制在某个区域,所以就要设置package keepin和route keepin。

扫码关注

扫码关注